“운영체제 : 아주 쉬운 세가지 이야기”를 읽으면서 핵심 내용을 정리하였습니다.

이화여대 반효경 교수님의 운영체제 강의를 듣고 복습 차원에서 책 한권을 완독해보고자 합니다.

잘못된 정보가 있다면 댓글 남겨주시면 감사하겠습니다!

페이징의 한계

페이징을 잘못 구현하면 큰 성능 저하가 올 수 있는데 이유는 아래와 같다

•

가상 주소 변환을 위해 주소 변환에 필요한 정보를 담고 있는 페이지 테이블을 접근(메모리 읽기 작업 느림)해야 되기 때문에 성능저하 발생

TLB 란?

페이징의 한계를 해결하기 위해 하드웨어의 도움을 받는다.

변환 색인 버퍼(translation-lookaside buffer, TLB)는 MMU의 일부로서 자주 참조되는 가상 주소의 변환 정보를 저장하는 하드웨어 캐시이다. 주소 변환 캐시(address-translation cache)라고도 부른다.

가상 메모리 참조시, 하드웨어는 먼저 TLB를 확인하게 된다.

TLB 기본 알고리즘

//하드웨어가 관리하는 TLB

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

(Success, TlbEntry) = TLB_Lookup(VPN)

if (Success == True)// TLB HIT

if (CanAccess(TlbEntry.ProtectBits) == True)

Offset = VirtualAddress & OFFSET_MASK

PhysAddr = (TlbEntry.PFN << SHIFT) | Offset

AccessMemory(PhysAddr)

else

RaiseException(PROTECTION_FAULT)

else// TLB MISS

PTEAddr = PTBR + (VPN * sizeof(PTE))

PTE = AccessMemory(PTEAddr)

if (PTE.Valid == False)

RaiseException(SEGMENTATION_FAULT)

else if (CanAccess(PTE.ProtectBits) == False)

RaiseException(PROTECTION_FAULT)

else

TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)

RetryInstruction()

C++

복사

1.

가상 주소로 부터 가상 페이지 번호를 추출한다.

2.

해당 가상 페이지 번호가 TLB에 들어있는지 확인한다.

3.

만약 TLB에 들어있다면 TLB에 들어있는 정보 기반으로 물리 주소 계산해서 접근

4.

만약 TLB에 들어있지 않다면 페이지 테이블에 접근하여 주소변환에 필요한 정보를 TLB에 갱신하고 해당 명령어를 재실행

예제

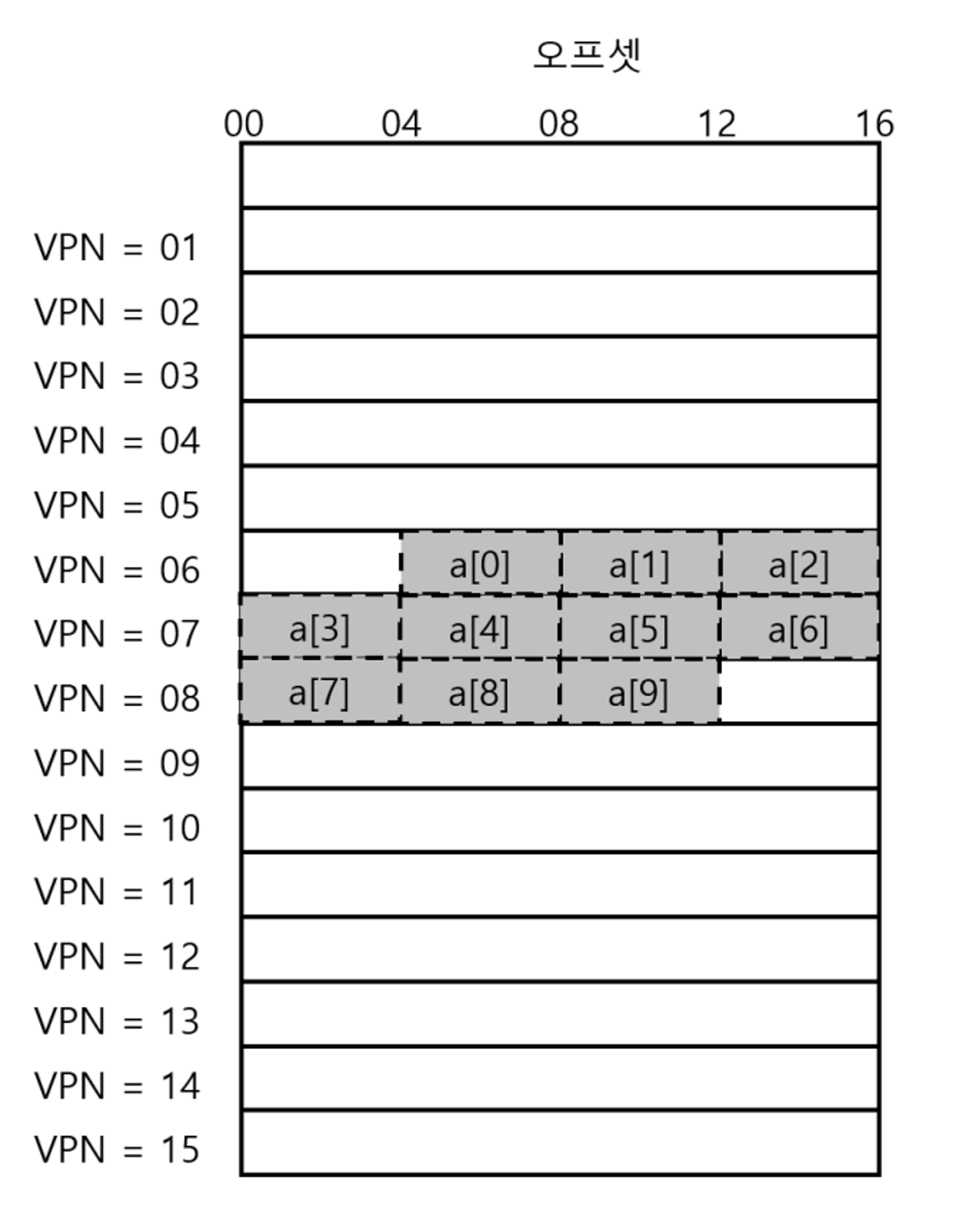

최초 a[0]에 접근하기 위해 TLB에서 VPN을 확인하면 정보가 없기 때문에 TLB miss가 일어나고 TLB정보 갱신이 일어난다. a[1], a[2]의 경우에는 공간 지역성으로 인해 TLB hit가 일어나게 된다. 만약 페이지의 크기가 더 크다면 TLB의 효과가 더 증가 할 것이다.

공간 지역성(spatial locality)

•

특정 데이터 x를 접근한 후 x에 인접한 메모리 주소를 접근할 확률이 높다는 사실에 근거함

시간 지역성(temporal locality)

•

한번 접근한 데이터는 다시 접근할 확률이 높다는 사실에 근거함

캐싱

컴퓨터 시스템에서 사용되는 가장 기본적인 성능 개선 기술 중 하나이다. 하드웨어 캐시의 근본 취지는 지역성을 활용하는 것이다.

지역성에는 앞서 설명한 시간 지역성, 공간지역성이 있다. 추가로 접근 지역성은 필요한 메모리의 내용을 매우 빠른 CPU칩 내의 메모리에 위치시키는 것이다.

TLB 미스 처리의 주체

하드웨어

•

CISC(complex instruction set computers)는 복잡한 하드웨어 명령어들로 구성된 컴퓨터 시스템을 말한다. 해당 시스템이서는 TLB 미스 처리를 하드웨어에서 처리한다. 하드웨어는 페이지 테이블에 대한 정보를 가지기 위해 page table base register를 가지고 있다.

소프트웨어

•

RISC(reduced intruction set computing)은 CISC보다 최근에 등장한 컴퓨터 구조이다. 해당 구조에서는 TLB 미스를 소프트웨어에서 처리한다. TLB 미스가 발생하면 하드웨어는 예외 시그널을 발생 시키고 운영체제의 커널 모드에서 트랩 핸들러가 실행된다. 이때 핸들러에서는 특권명령어를 사용하여 TLB에 접근하여 TLB정보를 갱신한다.

•

구현 시 중요 사항

◦

시스템콜과 달리 핸들러가 실행 된 이후 다음 명령어를 실행 하는 것이 아니라 현재 명령어를 재실행 하여야 하기 때문에 운영체제는 트랩의 발생 원인을 알고 있어야 하고 해당 원인에 따라 PC값을 어떻게 변경할지 정해야 한다.

◦

TLB 미스 핸들러를 실행 할때, TLB 미스가 무한 반복되지 않도록 주의 해야 한다. 만약 TLB 미스 핸들러를 접근하는 과정에서 TLB 미스가 일어나게 된다면 무한 루프에 빠지게 된다. 이를 해결하기 위한 두가지 방법은 아래와 같다.

▪

TLB 핸들러의 주소를 물리 주소로 표시한다. (주소 변환 없이 핸들러를 실행 시킬 수 있음)

▪

핸들러 코드 주소를 저장하는데 TLB의 일부를 영구히 할당한다.

TLB 구성

TLB는 완전 연관(fully associative) 방식으로 설계 된다. 해당 방식에서 원하는 변환 정보의 검색은 병렬적으로 수행된다.

TLB에는 VPN, PFN 이외에도 여러 정보들이 저장되는데 대표적으로 아래와 같다.

•

Valid Bit

◦

특정 항목이 유효한 변환 정보를 가지고 있는지 표현

•

Protection Bit

◦

페이지가 어떻게 접근될 수 있는지 표현(읽기, 쓰기, 실행)

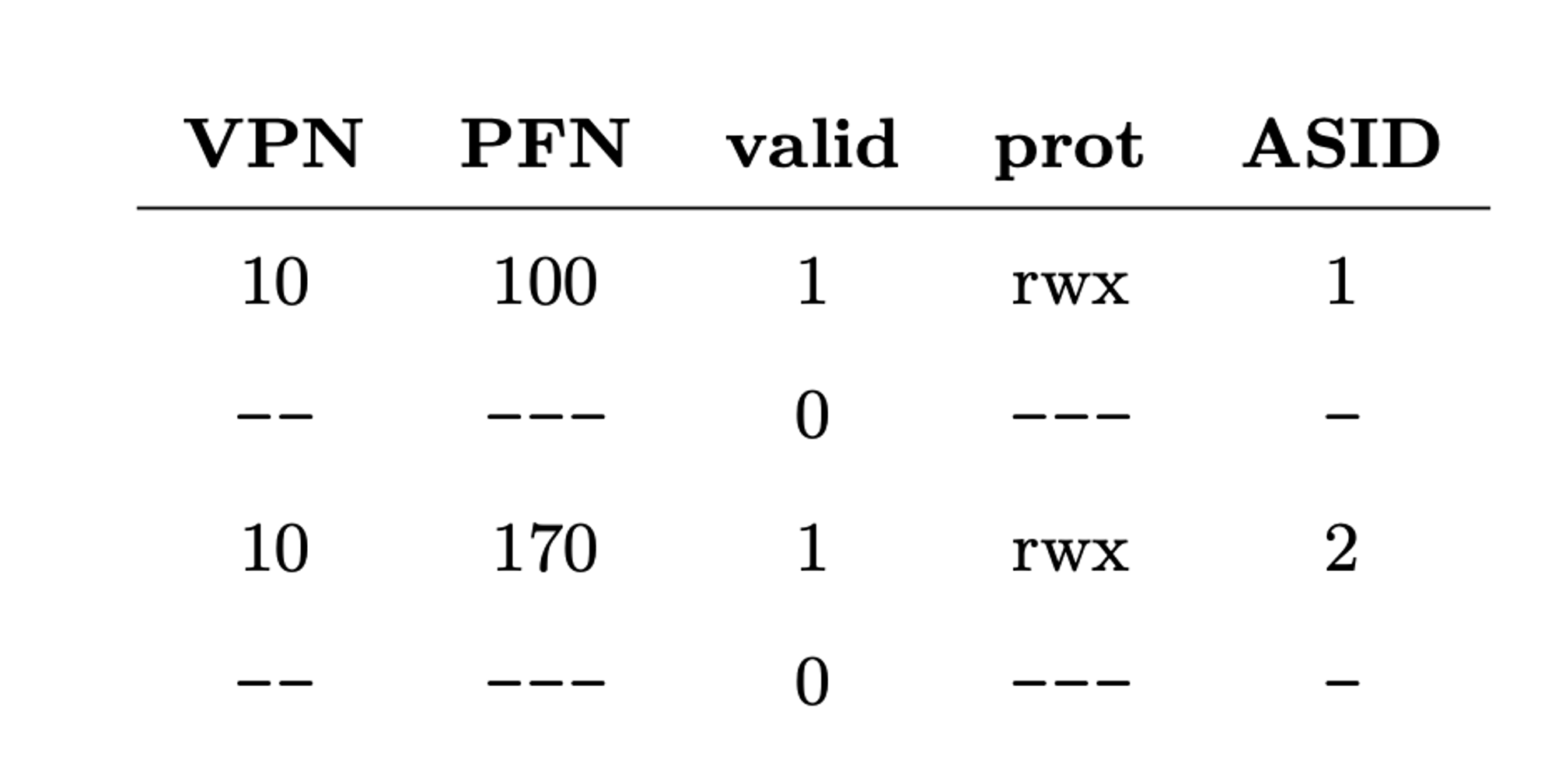

문맥 교환 시 TLB 교체

TLB내에 저장되어 있는 주소 변환 정보는 해당 정보를 탑재 시킨 프로세스에서만 유효하다. 따라서 문맥교환이 일어날 때 현재 TLB에 저장되어 있는 정보는 의미가 사라지게 된다. 해당 문제를 해결하기 위한 방법은 아래와 같다

•

Valid Bit을 0으로 만들어 TLB를 비우기

◦

문맥 교환이 자주 일어 난다면 코드페이지에 접근을 할때 마다 TLB 미스가 발생하므로 성능에 부담을 줌

•

주소 공간 식별자(address space identifier, ASID)를 추가

◦

프로세스 마다 TLB 변환 정보를 구분할 수 있게됨

◦

하드웨어는 현재 어떤 프로세스가 실행 중인지 알기 위해 별도의 레지스터가 필요함

TLB 교체 정책

TLB 캐시가 가득 찻을 때 어떤 부분을 교체해야 할지 정하는 정책이 필요하고 이는 디스크와 메모리 간의 페이지 스와핑 부분과 유사하다.

가장 대표적인 정책으로는 최저 사용 빈도(least-recently-used, LRU) 방식이 있다. 사용되지 않은 오래된 항목일수록 다음에 사용될 확률이 적다는 가정에 근거한다.